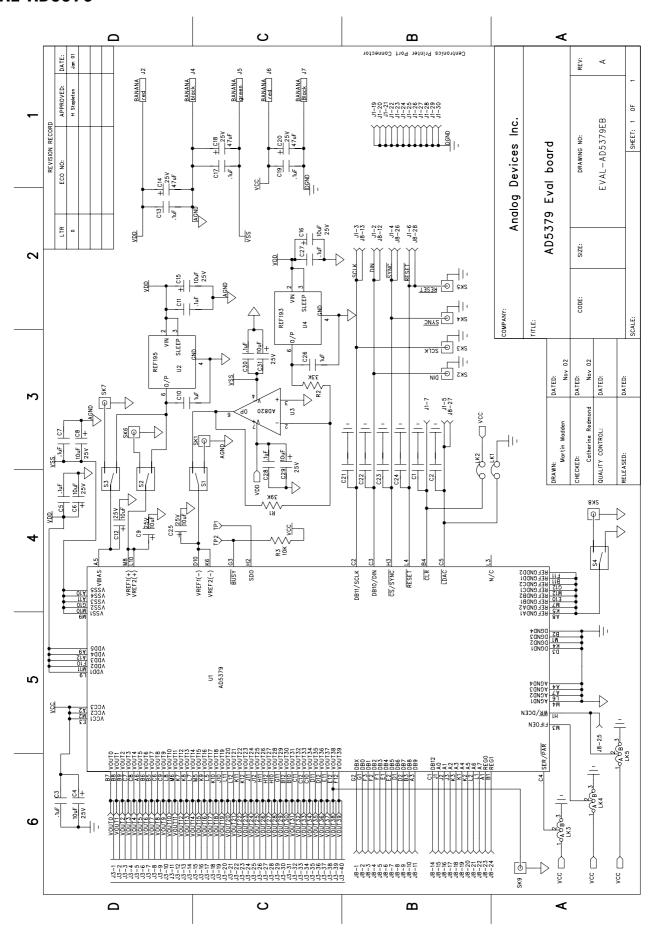

# Evaluation Board for AD5379, 40-Channel, 14-Bit, Parallel And Serial Input, Voltage-Output DAC

# **Preliminary Technical Data**

EVAL-AD5379

#### **FEATURES**

Full Featured Evaluation Board

On Board Reference and Buffers

Various Link Options

Direct Hook up to Printer Port of IC

PC Software for control of DACs

Socketed AD5379 for easy replacement

#### INTRODUCTION

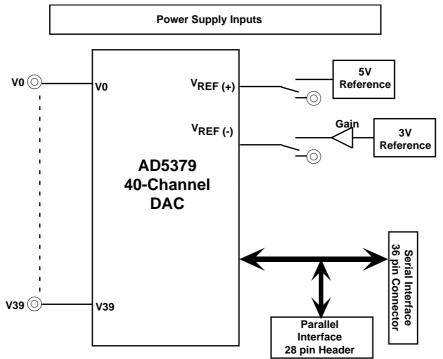

This Technical Note describes the evaluation board for the AD5379, 40 channel 14 bit DAC.

The AD5379 contains forty 14-bit DACs in one package. It has a maximum output voltage span of 17.5V which corresponds to an output range of -8.75 V to +8.75 V derived from reference voltages of -3.5 V and +5 V.

The AD5379 has a parallel interface in which 14 data-bits are loaded into one of the input registers under the control of the  $\overline{WR}$ ,  $\overline{CS}$  and DAC channel address pins, A0–A7. It also has a 3-wire serial interface which is compatible with SPI<sup>TM</sup>, QSPI<sup>TM</sup>, MICROWIRE<sup>TM</sup> and DSP interface standards.

The DAC outputs are updated on reception of new data into the DAC registers. All the outputs can be updated simultaneously by taking the  $\overline{\text{LDAC}}$  input low. Each channel has a programmable gain and offset adjust register.

Each DAC output is gained and buffered on-chip with respect to an external REFGND input. The DAC outputs can also be switched to REFGND via the  $\overline{\text{CLR}}$  pin.

Full data on the AD5379 may be found in the data sheet available from Analog Devices and should be consulted in conjunction with this Technical Note when using the Evaluation Board.

# **OPERATING THE AD5379 EVALUATION BOARD Power Supplies**

The following external supplies must be provided: + 5V between the  $V_{CC}$  and DGND inputs for the digital supply of the AD5379.  $V_{DD}$  and  $V_{SS}$  should be supplied with +/-12V respectively. Note that  $V_{DD}$  and Vss must provide sufficient headroom for the output voltage range.

Both AGND and DGND inputs are provided on the board. The AGND and DGND planes are connected at one location close to the AD5379. It is recommended not to connect AGND and DGND elsewhere in the system to avoid ground loop problems.

Each supply is decoupled to the relevant ground plane with  $47\mu F$  and  $0.1\mu F$  capacitors. Each device supply pin is again decoupled with a  $10\mu F$  and  $0.1\mu F$  capacitor pair to the relevant ground plane.

REV. PrC Mar '03

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# PRELIMINARY TECHNICAL DATA

# EVAL-AD5379

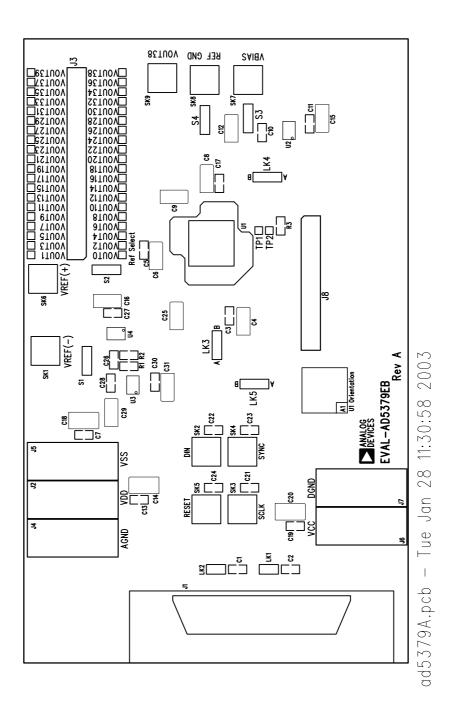

#### LINK OPTIONS

There are a number of link and switch options on the evaluation board which should be set for the required operating setup before using the board. The functions of these link and switch options are described in detail below.

| LIIIK 110. | runction                                                                                                           |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| LK1        | LDAC may be driven from the serial or parallel interface or tied permanently low allowing an automatic             |  |  |

|            | update of the DAC output once new data is latched.                                                                 |  |  |

| LK2        | This link allows the $\overline{\text{CLR}}$ input to be pulled high thus ensuring the DAC is in normal operation. |  |  |

| LK3        | Connect to the A position to select the Serial interface or to the B position for the Parallel interface.          |  |  |

| LK4        | Connect to the A position to enable the on chip FIFO, in position B, the FIFO is disabled.                         |  |  |

| LK5        | Dual function input. In parallel mode, the pin is the WR input, while in serial mode, the Daisy chain enable       |  |  |

|            | input, when connected to A, daisy chaining is enabled and disabled when LK5 connects to B.                         |  |  |

| S1         | Selects between on board -3.5V reference or an externally applied reference.                                       |  |  |

| S2         | Allows the user to select between the on board 5V reference or an external reference.                              |  |  |

| <b>S</b> 3 | When $V_{REF(+)} > 4.5V$ , the $V_{BIAS}$ pin must be overdriven. S3 enables it to be driven by the on board 5V    |  |  |

|            | reference or by an external reference.                                                                             |  |  |

|            |                                                                                                                    |  |  |

-2- REV. PrC

#### **EVALUATION BOARD SOFTWARE**

#### Software Installation

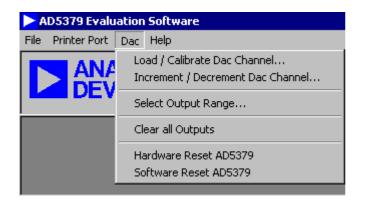

The AD5379 evaluation kit consists of self-installing software on CD-ROM. In the event of the setup file not running automatically, run the file setup.exe from the CD-ROM. Software is compatible with Win95 to Windows2000. Ensure that the Centronics cable connects the PC to the AD5379 eval board. Run ad5379.exe from the Analog Devices Menu. The main screen with drop down menus (File, Printer Port, DAC and Help) looks as follows:

The DAC menu allows control of the 40 DAC channels, in addition to other functions such as software or hardware RESET of the DAC channels and clearing the outputs.

#### Reference Selection

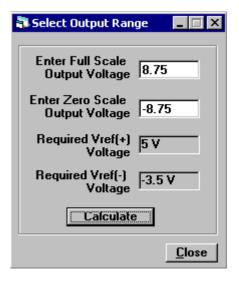

The voltages applied to  $V_{REF}(+)$  and  $V_{REF}(-)$  determine the output voltage range and span on VOUT0-VOUT39. If the offset and gain features are not used (m and c are left at their power-on values), the reference levels required can be calculated as follows:

```

V_{REF}(+)_{min} = (VOUT_{max} - VOUT_{min}) / 3.5

V_{REF}(-)_{max} = (AGND + VOUT_{min}) / 2.5

```

If the offset and gain features of the AD5379 are used, then the output range required is slightly different. Note that  $V_{\rm DD}$  and Vss must provide sufficient headroom.

In the DAC menu, choose the "Select Ouput Range" and enter the required full scale and zero scale output voltages, click on "calculate" and the software will suggest the negative and positive voltage to use.

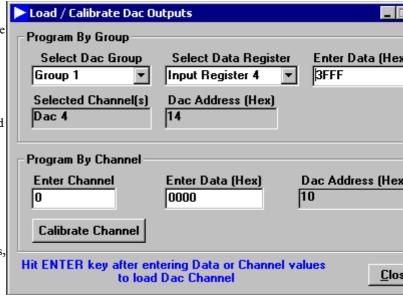

#### Load DAC Channels

Under the DAC menu, select the "Load/Calibrate DAC Channel option". All 40 channels or each channel or group of channels may be loaded with the entered DAC code. Remember to hit enter after entering data.

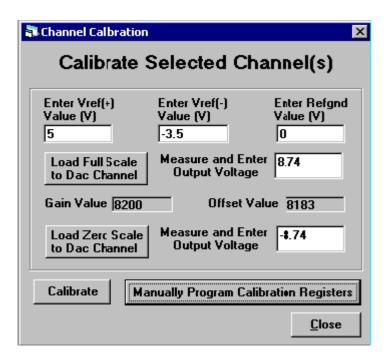

Click the calibrate channel button to enter the calibration window. Here, a number of values need to be entered. Enter the positive and negative reference values. Load Full scale and measure the output voltage on the relevant channel, input this into the calibration window. Now load zero scale and again enter the measured value in the appropriate field. Clicking the calibrate button calibrates the device to the required output voltage.

REV. PrC -3-

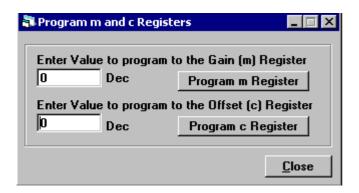

In addition, the user may manually calibrate the Gain and Offset registers.

#### Increment/Decrement Function

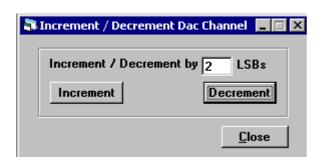

The AD5379 special function register enables the user to increment or decrement the internal 13Bit input register data in steps of 0 to 127 LSBs.

-4- REV. PrC

# PRELIMINARY TECHNICAL DATA

# EVAL-AD5379

| Component Listing |                                         |                                              |                          |  |

|-------------------|-----------------------------------------|----------------------------------------------|--------------------------|--|

| Qty               | Reference Designator                    | Description                                  | Supplier/Number          |  |

| 1                 | U1                                      | AD5379                                       | Analog Devices           |  |

|                   |                                         | Socket                                       | E-tec BPW108-1030-12AA01 |  |

| 1                 | U2                                      | REF195                                       | Analog Devices           |  |

| 1                 | U3                                      | AD820                                        | Analog Devices           |  |

| 1                 | U4                                      | REF193                                       | Analog Devices           |  |

| 1                 | R1                                      | 39K Res (0805 Package)                       | FEC 912-049              |  |

| 1                 | R2                                      | 33K Res (0805 Package)                       | FEC 912-037              |  |

| 1                 | R3                                      | 10K Res (0805 Package)                       | FEC 911-975              |  |

| 6                 | C1 C2 C21-C24                           | 470pF                                        | FEC 344-9026             |  |

| 9                 | C3 C5 C7 C11 C13 C17 C19 C27 C28        | 0.1uF Multilayer Ceramic Cap. (0805 Package) | FEC 499-687              |  |

| 2                 | C10 C26                                 | 1uF                                          | FEC 318-8899             |  |

| 9                 | C4 C6 C8 C9 C12 C15 C16 C25 C29         | 10uF 25V Tantalum Capacitor (TAJ-C Size)     | FEC 197-518              |  |

| 3                 | C14 C18 C20                             | 47uF 25V Tantalum Capacitor (TAJ-D Size)     | FEC 197-531              |  |

| 1                 | J1                                      | 36 Pin Centronics Connector (IEEE 488 Style) | FEC 147-753              |  |

| 2                 | J2 J6                                   | Red Banana Socket                            | FEC 150-039              |  |

| 2                 | J3                                      | HEADER40                                     | FEC 511-122              |  |

| 2                 | J4 J7                                   | Black Banana Socket                          | FEC 150-040              |  |

| 1                 | J5                                      | Green Banana Socket                          | FEC 150-041              |  |

| 1                 | J8                                      | HEADER28                                     | 511-122&511-080          |  |

| 2                 | LK1 LK2                                 | 2 Pin (SIL) Link Option (0.1" pitch)         | FEC 511-705              |  |

| 3                 | LK3-LK5                                 | JUMPER2\SIP3                                 | FEC 511-717              |  |

| 5                 | LK1-LK5                                 | Shorting Bar                                 | FEC 150-410              |  |

| 8                 | SK1-SK8                                 | Gold 50 Ohm SMB Jack                         | FEC 310-682              |  |

| 4                 | S1-S4                                   | SW/SPST/SIP                                  | FEC 733-647              |  |

| 42                | VOUT0-VOUT39 TP1 TP2                    | Black Testpoint                              | FEC 240-333              |  |

| 1                 | U2 U4                                   | Ultra low profile socket strip               | FEC 519-959              |  |

| 5                 | Each Corner and 1 under the BGA Socket. | Rubber Stick-On Feet                         | FEC 148-922              |  |

REV. PrC -5-

# PRELIMINARY TECHNICAL DATA

# EVAL-AD5379

REV. PrC -7-

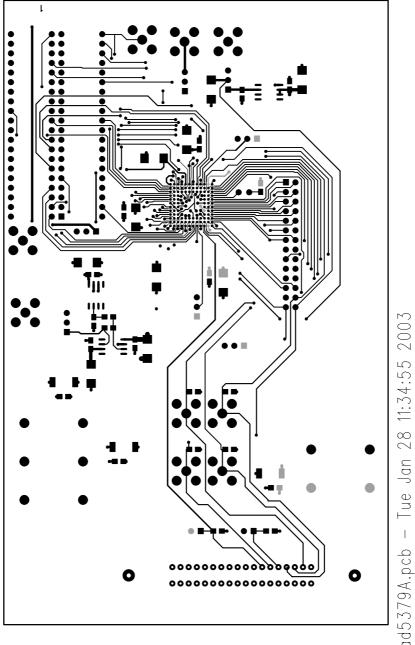

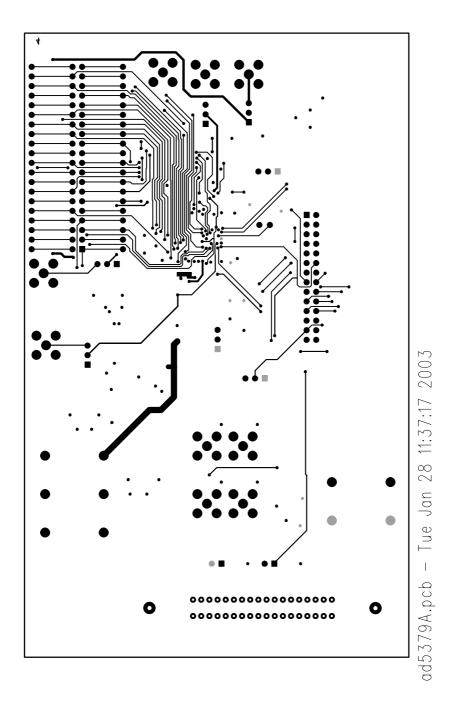

ad5379A.pcb

REV. PrC -9-